easics is a leading provider of custom ASIC / SoC design & supply services with +30 years in business. we enable our customers to bring their innovative products to market quickly and efficiently.

our services include everything from initial concept, requirements engineering, chip architecture, IP selection, design & verification, to prototyping (using FPGA and/or testchip), and characterization, manufacturing & test.

easics is an ISO 9001:2015 certified company.

your trustworthy ASIC / SoC design partner

long-term partner

support throughout your product lifecycle

priority access to the initial design team for support and new developments

many 10+ years customers

risk reduction

pre-project risk register and verification levels ensure on-time product launch

starting from-scratch or from customer legacy

third-party IP selection support

effective communication

we will update you on project progress, and promptly address any issues

efficient multi-site cooperation

ownership & accountability

taking responsibility for quality, schedule and budget

product families

we can design scalable / future-proof blocks to enable a product family of chips

security

our top-notch IT infrastructure protects your IP

our core business

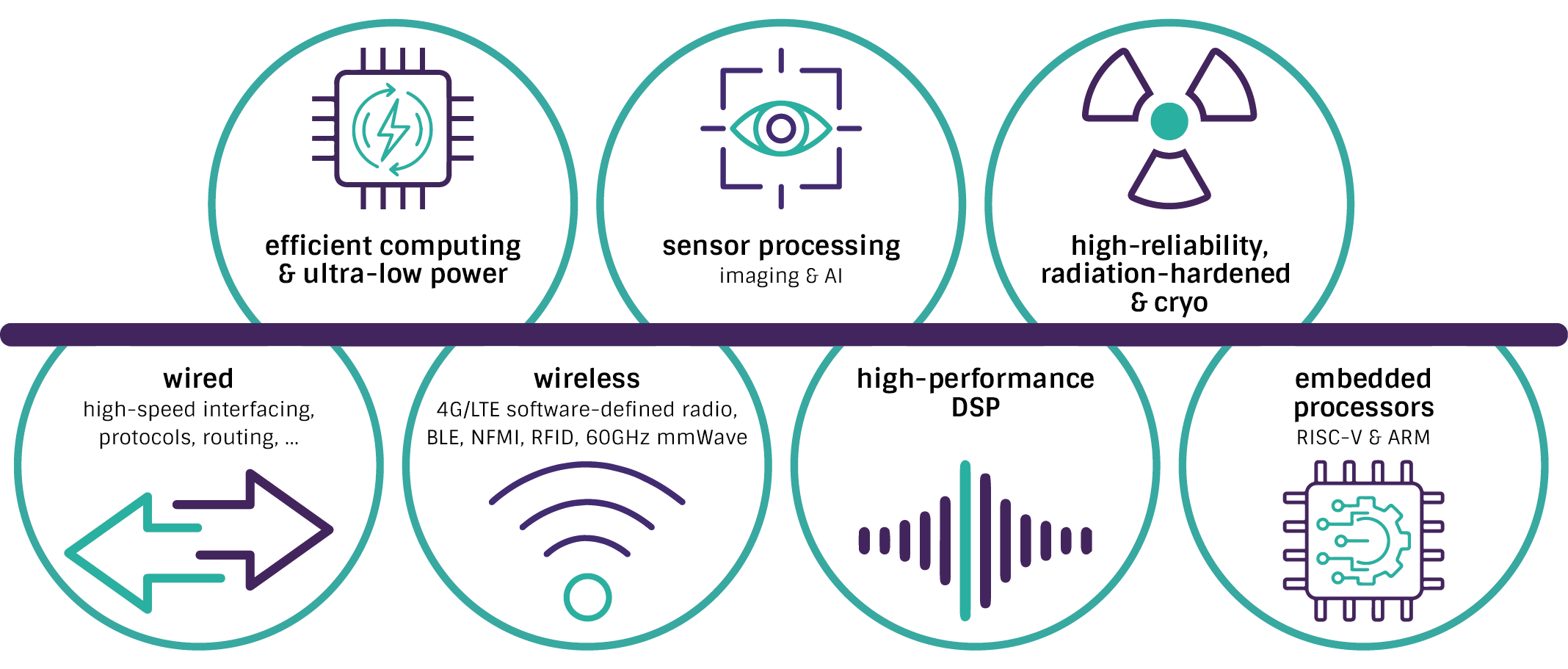

digital ASIC / SoC

design & verification

macro & full chip: RTL to GDSII

VHDL, Verilog, SystemVerilog, UVM, SystemC

PPA optimization

wreal, Verilog-AMS, UVM-AMS

ULP: clock gating, power gating

production test

Technology nodes

independent design house

We support a wide range of foundries, addressing our customers needs.

Both Synopsys and Cadence EDA flows are supported, ensuring compatibility in every project.

what people say?

In working with easics, we have found a proficient and reliable partner for designing the digital core of our sensor readout. We appreciate their dedication to meeting deadlines and providing support throughout the development process. easics has consistently delivered high-quality, customizable designs that are compliant with our specific requirements. easics’ exceptional in-house expertise has been a key factor in our success.

Rosa Maria Vinella

VP Sensors Product Management

easics and imec.IC-link have built a strong partnership over the past 10 years in ASIC design and IP, with a focus on ASIC design. easics’ exceptional in-house expertise has been a key factor in our success in delivering full-turnkey ASIC projects for a diverse range of clients, from small startups to large multinational companies. easics is located only a stone’s throw away from the imec headquarters, allowing for very efficient collaboration. Our customers have consistently provided positive feedback on easics' ability to think holistically, across a wide range of applications, including imaging, networking, and embedded code. We are excited to continue this partnership for years to come.

Steven Redant

Director

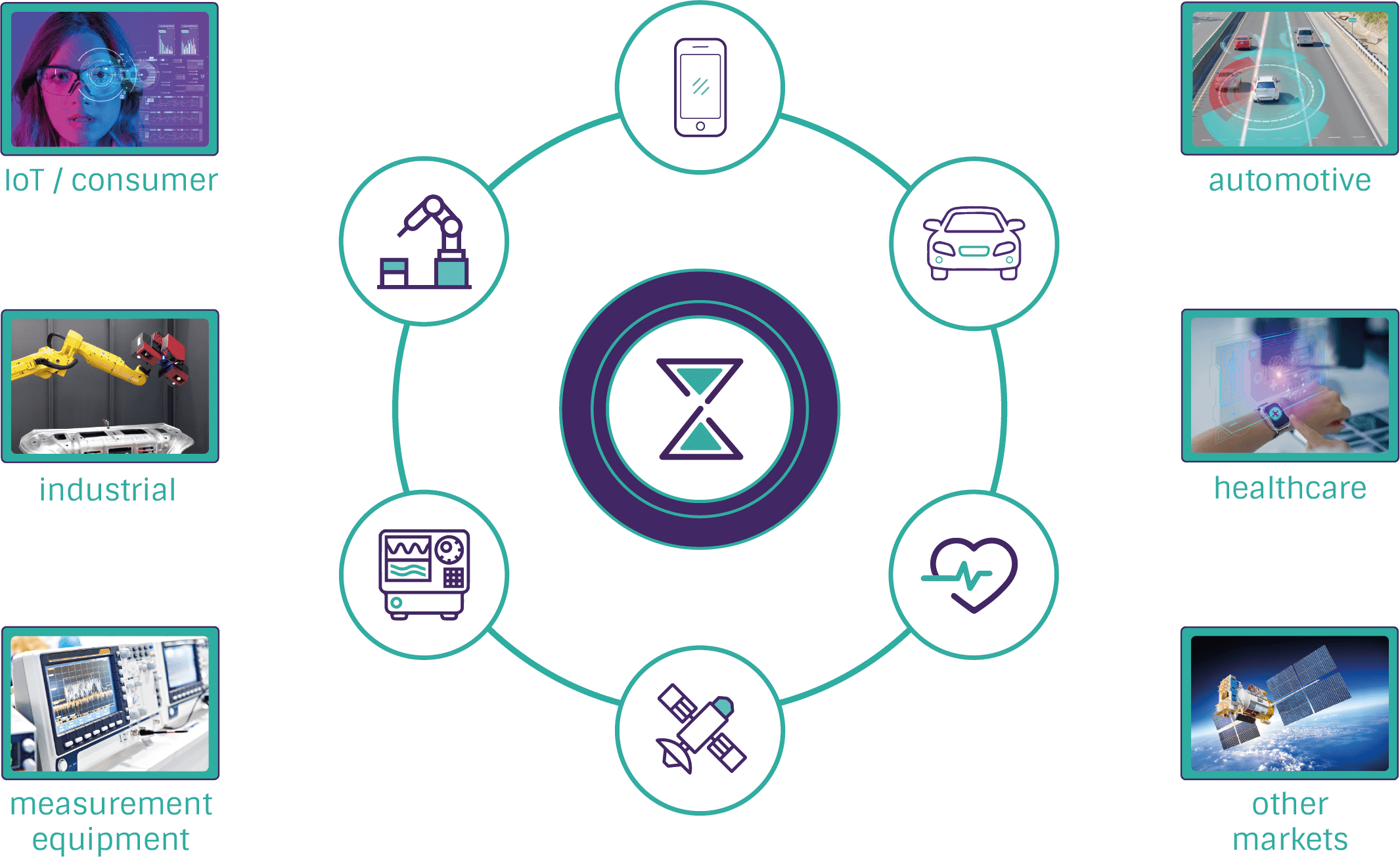

case studies

A flexible and scalable solution for better transition which can also be adapted for future design

Designing the digital section of the ASIC for radiation hardness + the test system development

Created and verified the RTL of the a first-time right bluetooth packet processor

Modeled, implemented and verified proprietary digital pixel processing algorithms

some of our clients

driving technology for leading brands

first-time right

feel free to get in touch with us

complete the form below and we will contact you within 48h

start the collaboration with us

and we will deliver the best solution

based on your needs

and we will deliver the best solution

based on your needs

easics nv

diestsevest 32 box 2b

3000 leuven, belgium

diestsevest 32 box 2b

3000 leuven, belgium

vat: BE 0444.501.015

services

products

solutions

© 2024 easics NV. All Rights Reserved – Privacy Policy