ASIC design for ESA

ASIC design for ESA

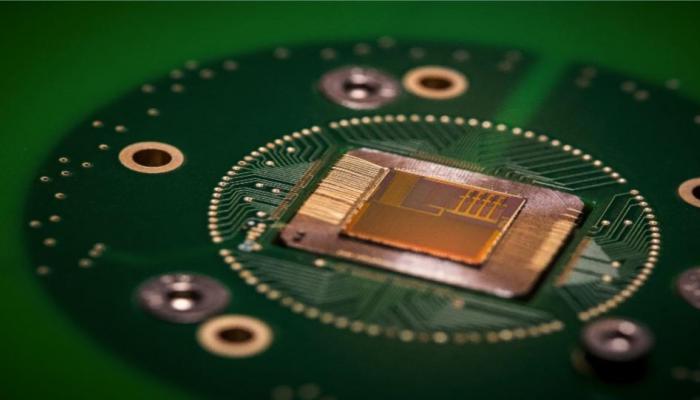

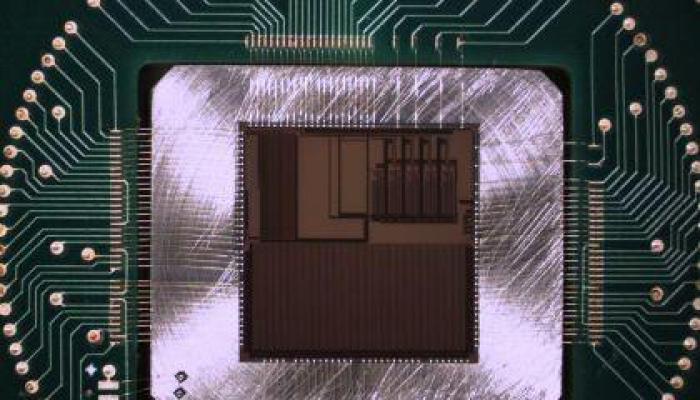

Caeleste, Easics and SELEX Galileo signed an ESA contract for the Development of a Prototype ASIC for Large Format NIR/SWIR Detector Array

The European consortium formed by the companies Caeleste (Belgium), easics (Belgium) and SELEX Galileo (United Kingdom) won the European Space Agency ’s call for tender AO/1-6814 Development of Prototype ASIC for Large Format Cryogenic NIR/SWIR (Near / Short Wave Infrared) Detector Arrays.

The ASIC is targeted for use in ESA’s future Space Science and Earth Observation missions. Its 18 month development aims to design an ASIC dedicated to large format cryogenic NIR/SWIR Detector. It will simplify the design of infrared instruments for space applications.

The complex presents several challenging features:

- 77K operation temperature

- Radiation hardness

- Fully programmable sequencer on chip

- 16-bits analog to digital conversion chain

The ASIC will allow cryogenic operation down to 77K, as well as at slightly higher temperature (120K), and even at room temperature with limited performance. This will allow system builders to trade off performance and thermal budget. The aim is to tailor the ASIC to a larger variety of devices, including CMOS and CCD image sensors by integrating PGAs (programmable gain amplifiers) and CDS (correlated double sampling). Of course, the sequencer is programmable for these purposes too.

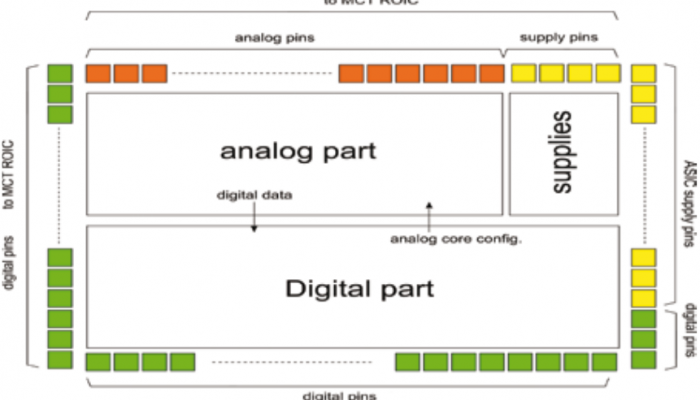

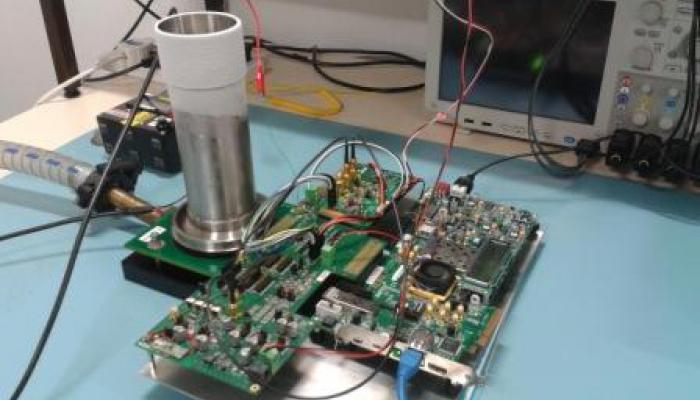

The project will benefit from the experience of each consortium partner. Caeleste is responsible for the project supervision and the design of the analog section of the ASIC. Easics is designing the digital section of the ASIC using imec standard DARE library for radiation hardness . Easics is also in charge of the FPGA-based test system development. SELEX Galileo joins as IR/cryogenic expert and will provide support for cryogenic operation, test and evaluation.

It is Caeleste’s aim to work together with infrared image sensor suppliers to develop key circuitries to improve the overall infrared imaging chain. The development of this ASIC fits in that scope. Indeed, Europe has a vast offer of high-end infrared sensors both in cooled and uncooled domains. But there are very few ASICs that can handle the dataflow and supply the corresponding sequence of signals necessary to operate the sensors. This is especially true in space applications.

This development fits in easics’ strategy to focus on System-on-Chip developments for markets and applications demanding high reliability, high-performance and future-proofness. Moreover, imaging is one of easics’ areas of expertise.

Download: DSP Valley newsletter 6.pdf