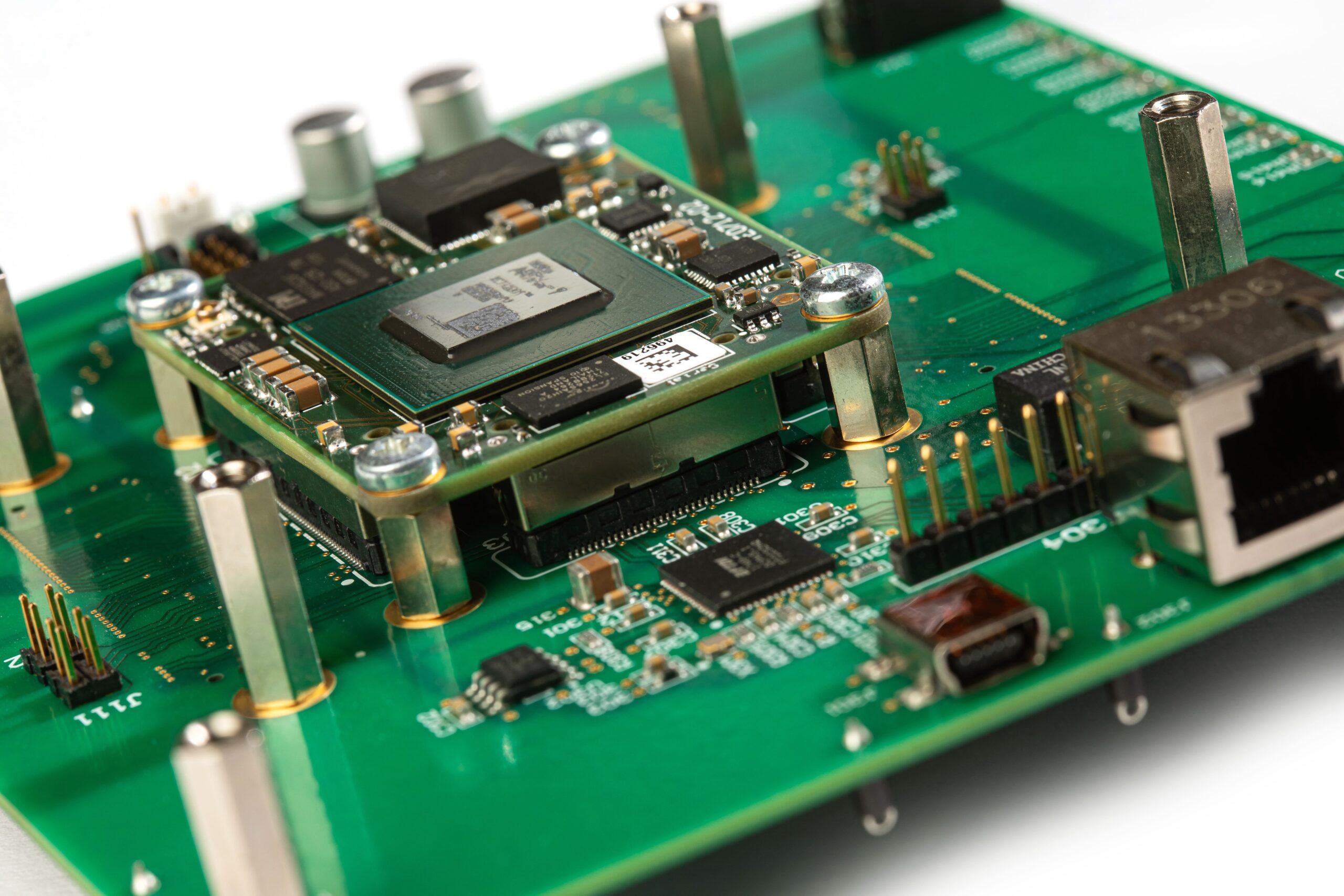

Image sensor read out on FPGA

Image sensor read out on FPGA

Overview

We are planning to use an FPGA to read out the data from an image sensor and transfer the data to the PC. Due to internal resources we would need external support.

Major company that is developing and producing measuring instruments for a large number of industries.

| Tags | FPGA design, Test & measurement, vision |

| Share |

Requirements

Our solution

Design: block-level architecture, pin planning, test & verification plan

Assist the customer with the FPGA board selection and board level architecture;

the requirements and specification document for easics FPGA logic; assessment of the existing Verilog code; the block-level architecture of the FPGA and the pin-planning of the FPGA

Implementation: RTL code and simulations via the test benches

Provide a verification test plan for the easics FPGA logic. easics will verify the Verilog FPGA code on the test setup with SystemC or UVM SystemVerilog.

Test and integration of the FPGA code on the electronics

Integration testing of the FPGA board in the system.

Results:

In a few months easics provided a working solution for the readout of the image sensor. The images were sent to the PC over USB 3.0.

Architecture document

Verification plan

FPGA bit streams

Software source code

Test benches

Simulation and synthesis scripts

SystemC simulation environment