# IP cores for ultra-low power Al-enabled chips

each nearbAI core is an ultra-low power neural processing unit (NPU) and comes with an optimizer / neural network compiler. it provides immediate visual and spatial feedback based on sensory inputs, which is a necessity for live augmentation of the human senses.

- > optimized neural network inferencing for visual, spatial and other applications

- > unparalleled flexibility: customized & optimized for the customer's use case

- ▶ produces the most optimal NPU IP core for the customer's use case: power, area, latency and memories trade-off

IRIS

ID

minimized development & integration time

# *ideal for battery-powered mobile, XR and IoT devices*

www.nearbai.com

## why nearbAI?

#### highly computationally efficient and flexible NPUs

enable lightweight devices with long battery life ... with ultra-low power, run heavily optimized AI-based functions locally

enable truly immersive experiences ... achieve sensors-to-displays latency within the response time of the human senses

enable smart and flexible capabilities ... fill the gap between "swiss-army knife" XR / AI mobile processor chips and limited-capability edge IoT / AI chips

# IP cores for ultra-low power Al-enabled chips

#### optimized for customer-specific use case

#### specifications

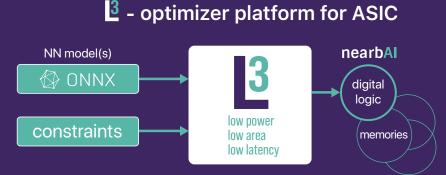

- L3 optimizer for optimal power, area and latency balance

- NN compiler for firmware updates in the field

- zero-latency NN switching e.g., face ID NN gets faces only from face detection NN, multiplexed with other NNs

- top computational efficiency for crystallized Al functions, yet programmable and field-upgradable

- configurable MAC accuracy: independent coefficient and data quantization, 4 to 16-bit, single-bit granularity

- long-term support: 5+ years

- power: supports sub 1 mW always-on visual / spatial applications

- configurable number of parallel MACs in convolution engine: 16 to 8192

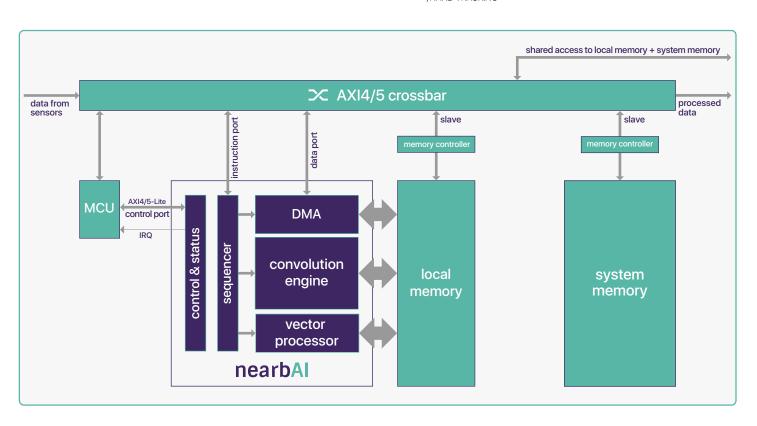

- integrates seamlessly with a wide range of RISC-V and ARM processor cores

- typ. 4nm for mobile XR processor chip

- typ. 22nm for compact extreme edge AI chip

- supports model zoo of CNN / RNN / LSTM, and tailored customization

for additional information, please contact your local sales representative

#### process

#### delivery options incl. customization

- standard off-the-shelf IP core(s)

- customized IP core(s)

- ▶ IP core(s) + ASIC integration services

- ▶ IP core(s) + full ASIC design services

### easics hq

diestsevest 32 box 2B 3000 leuven, belgium

tel: +32 16 395 611 e-mail: contact@easics.com

### let's do a custom benchmark together:

provide us with your use case:

#### • quantized or unquantized NN model(s):

ONNX, TensorFlow (Lite), PyTorch, or Keras

#### • constraints:

average power & energy per inference, silicon area, latency, memories, frame rate, image resolution, foundry + technology node

easics us

/1.3

e-mail: contact-us@easics.com